Attributes

Part Number

MCP65R41T-2402E/CHY

Spice Model

MCP65R41_1202

Manufacturer

Microchip

Spice Library

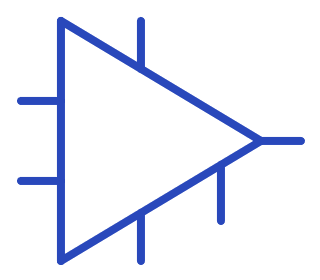

.SUBCKT MCP65R41_1202 1 2 3 4 5 6

* | | | | | |

* | | | | | VRef

* | | | | Output

* | | | Negative Supply

* | | Positive Supply

* | Inverting Input

* Non-inverting Input

*

********************************************************************************

* Software License Agreement *

* *

* The software supplied herewith by Microchip Technology Incorporated (the *

* 'Company') is intended and supplied to you, the Company's customer, for use *

* soley and exclusively on Microchip products. *

* *

* The software is owned by the Company and/or its supplier, and is protected *

* under applicable copyright laws. All rights are reserved. Any use in *

* violation of the foregoing restrictions may subject the user to criminal *

* sanctions under applicable laws, as well as to civil liability for the *

* breach of the terms and conditions of this license. *

* *

* THIS SOFTWARE IS PROVIDED IN AN 'AS IS' CONDITION. NO WARRANTIES, WHETHER *

* EXPRESS, IMPLIED OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED *

* WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO *

* THIS SOFTWARE. THE COMPANY SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR *

* SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER. *

********************************************************************************

*

* The following op-amps are covered by this model:

* MCP65R41_1202

*

*

* Revision History:

* REV A: 18-May-11, Created model

*

*

*

*

* Recommendations:

* Use PSPICE (or SPICE 2G6; other simulators may require translation)

* For a quick, effective design, use a combination of: data sheet

* specs, bench testing, and simulations with this macromodel

* For high impedance circuits, set GMIN=100F in the .OPTIONS statement

* Can disable Hysteresis for faster response in large circuits by adding comments

* in front of statements flagged below

*

* Supported:

* Typical performance for temperature range (-40 to 125) degrees Celsius

* DC, AC, Transient, and Noise analyses.

* Most specs, including: offsets, DC PSRR, DC CMRR, input impedance,

* open loop gain, voltage ranges, supply current, ... , etc.

* Temperature effects for Ibias, Iquiescent, Iout short circuit

* current, Vsat on both rails, Slew Rate vs. Temp and P.S.

*

*

*

* Input Stage

*

V10 3 10 -500M

R10 10 11 218K

R11 10 12 218K

G10 10 11 10 11 458U

G11 10 12 10 12 458U

C11 11 12 1.82E-15

C12 1 0 4.00P

*E12 71 14 POLY(6) 20 0 21 0 22 0 23 0 26 0 27 0 0.00 49.3K 49.3K 49.3K 49.3K 1 1

E12 71 14 POLY(7) 20 0 21 0 22 0 23 0 26 0 27 0 111 0

+ 0.00 55 55 15 15 1 1 -.5M

*+ 1.5M 55 55 15 15 1 1 -.5M

* LINE ABOVE FOR HYSTERESIS, LINE BELOW FOR NO HYSTERESIS

*+ 1.5M 55 55 15 15 1 1 0

G12 1 0 62 0 1m

G13 1 2 63 0 1u

M12 11 14 15 15 NMI

M14 12 2 15 15 NMI

G14 2 0 62 0 1m

C14 2 0 4.00P

I15 15 4 500U

V16 16 4 -300M

GD16 16 1 TABLE {V(16,1)} ((-100,-100E-15)(0,0)(1m,1u)(2m,1m))

V13 3 13 -300M

GD13 2 13 TABLE {V(2,13)} ((-100,-100E-15)(0,0)(1m,1u)(2m,1m))

R71 1 0 10.0E12

R72 2 0 10.0E12

R73 1 2 10.0E12

C13 1 2 2.00P

*

* Noise, PSRR, and CMRR

*

I20 21 20 423U

D20 20 0 DN1

D21 0 21 DN1

I22 22 23 1N

R22 22 0 1k

R23 0 23 1k

G26 0 26 POLY(2) 3 0 4 0 0.00 -70.7U -125U

R26 26 0 1

G27 0 27 POLY(2) 1 0 2 0 -2.19M 125U 125U

R27 27 0 1

*

* Open Loop Gain, Slew Rate

*

G30 0 30 12 11 1

R30 30 0 1.00K

G31 0 31 3 4 18.6

I31 0 31 DC -82.1M

R31 31 0 1 TC=0.00,0.00

GD31 30 0 TABLE {V(30,31)} ((-100,-1n)(0,0)(1m,0.1)(2m,2))

G32 32 0 3 4 18.6

I32 32 0 DC -82.1M

R32 32 0 1 TC=0.00,0.00

GD32 0 30 TABLE {V(30,32)} ((-2m,2)(-1m,0.1)(0,0)(100,-1n))

G33 0 33 30 0 1m

R33 33 0 1K

G34 0 34 33 0 1.00

R34 34 0 1K

C34 34 0 15.9U

G37 0 37 34 0 1m

R37 37 0 1K

C37 37 0 15.9E-15

G38 0 38 37 0 1m

R38 39 0 1K

L38 38 39 15.9N

E38 35 0 38 0 1

G35 33 0 TABLE {V(35,3)} ((-1,-1n)(0,0)(2.00,1n))(2.2,1))

G36 33 0 TABLE {V(35,4)} ((-2.2,-1)((-2.00,-1n)(0,0)(1,1n))

*

* Output Stage

*

R80 50 0 100MEG

G50 0 50 57 96 2

R58 57 96 0.50

R57 57 0 10.0

C58 5 0 2.00P

G57 0 57 POLY(3) 3 0 4 0 35 0 0 37.5M 50.0M 100M

GD55 55 57 TABLE {V(55,57)} ((-2m,-1)(-1m,-1m)(0,0)(10,1n))

GD56 57 56 TABLE {V(57,56)} ((-2m,-1)(-1m,-1m)(0,0)(10,1n))

E55 55 0 POLY(2) 3 0 51 0 4.7M 1 -48.5M

E56 56 0 POLY(2) 4 0 52 0 9.9M 1 -36.5M

R51 51 0 1k

R52 52 0 1k

GD51 50 51 TABLE {V(50,51)} ((-10,-1n)(0,0)(1m,1m)(2m,1))

GD52 50 52 TABLE {V(50,52)} ((-2m,-1)(-1m,-1m)(0,0)(10,1n))

G53 3 0 POLY(1) 51 0 -500U 1M

G54 0 4 POLY(1) 52 0 -500U -1M

*

* Current Limit

*

G99 96 5 99 0 1

R98 0 98 1 TC=-2.45M,-4.74U

G97 0 98 TABLE { V(96,5) } ((-11.0,-14.0M)(-1.00M,-13.8M)(0,0)(1.00M,13.8M)(11.0,14.0M))

*E97 99 0 VALUE { V(98)*((V(3)-V(4))*738M + -1.21)}

E97 99 0 VALUE { V(98)*LIMIT(((V(3)-V(4))*738M + -1.21),0.00,1E6)}

D98 4 5 DESD

D99 5 3 DESD

*

* Temperature / Voltage Sensitive IQuiscent

*

R61 0 61 1 TC=3.54M,-1.28U

G61 3 4 61 0 1

G60 0 61 TABLE {V(3, 4)}

*+ ((0,0)(600M,25.1N)(1.8,2.5U)(2.00,2.5U)

+ ((0,0)(600M,25.1N)(0.85,0.50u)(1.15,2.5u)(1.2,3u)(1.35,3.7u)(1.4,3.8u)(1.45,3.7u)(1.5,2.5u)(1.8,2.5U)(2.00,2.5U)

+ (3.00,2.5U)(5.00,2.51U)(6.00,2.52U))

*

* Temperature Sensitive offset voltage

*

I73 0 70 DC 1uA

*R74 0 70 1 TC=10.0

R74 0 70 1 TC=0.00

E75 1 71 70 0 1

*

* Temp Sensistive IBias

*

I62 0 62 DC 1uA

R62 0 62 REXP 349.81393U

*

* Temp Sensistive Offset IBias

*

I63 0 63 DC 1uA

R63 0 63 200M TC=12.0M,128U

*

* Hysteresis

*

G110 0 110 POLY(2) 3 0 4 0 10.4 -50M 50M

R110 110 0 1 TC=0.5M,0

E111 111 0 VALUE { V(110) * V(112) }

E112 112 0 TABLE {V(120,0)} ((-1,1)(-1m,0.99)(1m,-0.99)(1,-1))

C120 120 0 1u

G120 0 120 TABLE {V(57,4)} ((-1m,-1)(1m,1))

R120 0 120 1

C121 121 120 2p

C122 122 120 2p

V121 121 0 1

V122 122 0 -1

* Node 120 above is output of FF. Can substitute with node 57 for

* direct input from output state.

*

* Begin - VRef Subcircuit Added 05-16-11

*

R200 4 200 1 TC=3.35e-5,-4.55e-7

E200 201 4 200 4 1

VF200 202 6 0

F200 3 4 VF200 1

G200 201 202 TABLE { V(201, 202) }

+ ( (-5.5,-0.010)(-1u,-500u)(0,0) (1u,500u)(5.5,0.012) )

G201 4 200 TABLE { V(3, 4) }

+ ( (0,0)(1.3,1.185)

+ (1.31,1.195)(1.33,1.210)(1.35,1.220)(1.375,1.225)(1.387,1.225)(1.4,1.227)(1.440,1.225)(1.5,1.220)(1.58,1.2125)(5.5,1.2125))

*

* End - VRef Subcircuit

*

* Models

.MODEL NMI NMOS(L=2.00U W=42.0U KP=20.0U LEVEL=1 )

.MODEL DESD D N=1 IS=1.00E-15

.MODEL DN1 D IS=1P KF=50.0P AF=1

.MODEL REXP RES TCE= 7.71929

.ENDS MCP65R41_1202

Description

COMPARATOR 2.4V REF SOT-23-6

Spice Device Type

subcircuit

Prefix

U

Volume Pricing

$0.31