Attributes

Part Number

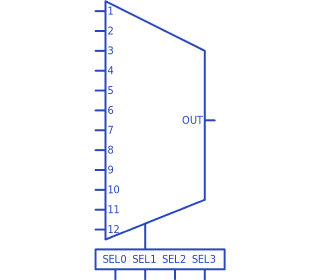

cMUX

6 Verilogams Port In8

9 - 9

Manufacturer

ViaDesigner

6 Verilogams Port In7

8 - 8

Description

No description

6 Verilogams Port In6

7 - 7

Prefix

U

6 Verilogams Port In5

6 - 6

Lead Free

Unknown

6 Verilogams Port In4

5 - 5

Package

6 Verilogams Port In3

4 - 4

Configuration Iframe Url

https://wizards.viadesigner.com/Wizard/GenWizardUpverter?wizardName=cMux_test

6 Verilogams Port In2

3 - 3

RoHS

Unknown

6 Verilogams Port In1

2 - 2

Approved Alternate Part Number

6 Verilogams Port In0

1 - 1

Mfg Package Ident

6 Verilogams Param Con

0

12 Verilogams Port Outn

18 - OUTN

6 Verilogams Param Coff

20f

12 Verilogams Port Cb3

16 - SEL3

6 Verilogams Param Roff

1T

12 Verilogams Port Cb2

15 - SEL2

6 Verilogams Param Ron

0.001

12 Verilogams Port Cb1

14 - SEL1

6 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

12 Verilogams Port Cb0

13 - SEL0

6 Verilogams Module

AMUXN1

12 Verilogams Port Out

17 - OUT

5 Verilogams Port Cb3

16 - SEL3

12 Verilogams Port In11

12 - 12

5 Verilogams Port Cb2

15 - SEL2

12 Verilogams Port In10

11 - 11

5 Verilogams Port Cb1

14 - SEL1

12 Verilogams Port In9

10 - 10

5 Verilogams Port Cb0

13 - SEL0

12 Verilogams Port In8

9 - 9

5 Verilogams Port Out

17 - OUT

12 Verilogams Port In7

8 - 8

5 Verilogams Port In11

12 - 12

12 Verilogams Port In6

7 - 7

5 Verilogams Port In10

11 - 11

12 Verilogams Port In5

6 - 6

5 Verilogams Port In9

10 - 10

12 Verilogams Port In4

5 - 5

5 Verilogams Port In8

9 - 9

12 Verilogams Port In3

4 - 4

5 Verilogams Port In7

8 - 8

12 Verilogams Port In2

3 - 3

5 Verilogams Port In6

7 - 7

12 Verilogams Port In1

2 - 2

5 Verilogams Port In5

6 - 6

12 Verilogams Port In0

1 - 1

5 Verilogams Port In4

5 - 5

12 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, outN, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, outN CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

5 Verilogams Port In3

4 - 4

12 Verilogams Module

AMUXN1

5 Verilogams Port In2

3 - 3

11 Verilogams Port Cb3

16 - SEL3

5 Verilogams Port In1

2 - 2

11 Verilogams Port Cb2

15 - SEL2

5 Verilogams Port In0

1 - 1

11 Verilogams Port Cb1

14 - SEL1

5 Verilogams Param Con

0

11 Verilogams Port Cb0

13 - SEL0

5 Verilogams Param Coff

20f

11 Verilogams Port Out

17 - OUT

5 Verilogams Param Roff

1T

11 Verilogams Port In11

11 - 11

5 Verilogams Param Ron

0.001

11 Verilogams Port In10

11 - 11

5 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

11 Verilogams Port In9

10 - 10

5 Verilogams Module

AMUXN1

11 Verilogams Port In8

9 - 9

4 Verilogams Port Cb3

16 - SEL3

11 Verilogams Port In7

8 - 8

4 Verilogams Port Cb2

15 - SEL2

11 Verilogams Port In6

7 - 7

4 Verilogams Port Cb1

14 - SEL1

11 Verilogams Port In5

6 - 6

4 Verilogams Port Cb0

13 - SEL0

11 Verilogams Port In4

5 - 5

4 Verilogams Port Out

17 - OUT

11 Verilogams Port In3

4 - 4

4 Verilogams Port In11

12 - 12

11 Verilogams Port In2

3 - 3

4 Verilogams Port In10

11 - 11

11 Verilogams Port In1

2 - 2

4 Verilogams Port In9

10 - 10

11 Verilogams Port In0

1 - 1

4 Verilogams Port In8

9 - 9

11 Verilogams Param Con

0

4 Verilogams Port In7

8 - 8

11 Verilogams Param Coff

20f

4 Verilogams Port In6

7 - 7

11 Verilogams Param Roff

1T

4 Verilogams Port In5

6 - 6

11 Verilogams Param Ron

0.001

4 Verilogams Port In4

5 - 5

11 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

4 Verilogams Port In3

4 - 4

11 Verilogams Module

AMUXN1

4 Verilogams Port In2

3 - 3

10 Verilogams Port Cb3

16 - SEL3

4 Verilogams Port In1

2 - 2

10 Verilogams Port Cb2

15 - SEL2

4 Verilogams Port In0

1 - 1

10 Verilogams Port Cb1

14 - SEL1

4 Verilogams Param Con

0

10 Verilogams Port Cb0

13 - SEL0

4 Verilogams Param Coff

20f

10 Verilogams Port Out

17 - OUT

4 Verilogams Param Roff

1T

10 Verilogams Port In11

12 - 12

4 Verilogams Param Ron

0.001

10 Verilogams Port In10

11 - 11

4 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

10 Verilogams Port In9

10 - 10

4 Verilogams Module

AMUXN1

10 Verilogams Port In8

9 - 9

3 Verilogams Port Cb3

16 - SEL3

10 Verilogams Port In7

8 - 8

3 Verilogams Port Cb2

15 - SEL2

10 Verilogams Port In6

7 - 7

3 Verilogams Port Cb1

14 - SEL1

10 Verilogams Port In5

6 - 6

3 Verilogams Port Cb0

13 - SEL0

10 Verilogams Port In4

5 - 5

3 Verilogams Port Out

17 - OUT

10 Verilogams Port In3

4 - 4

3 Verilogams Port In11

12 - 12

10 Verilogams Port In2

3 - 3

3 Verilogams Port In10

11 - 11

10 Verilogams Port In1

2 - 2

3 Verilogams Port In9

10 - 10

10 Verilogams Port In0

1 - 1

3 Verilogams Port In8

9 - 9

10 Verilogams Param Con

0

3 Verilogams Port In7

8 - 8

10 Verilogams Param Coff

20f

3 Verilogams Port In6

7 - 7

10 Verilogams Param Roff

1T

3 Verilogams Port In5

6 - 6

10 Verilogams Param Ron

0.001

3 Verilogams Port In4

5 - 5

10 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

3 Verilogams Port In3

4 - 4

10 Verilogams Module

AMUXN1

3 Verilogams Port In2

3 - 3

9 Verilogams Port Cb3

16 - SEL3

3 Verilogams Port In1

2 - 2

9 Verilogams Port Cb2

15 - SEL2

3 Verilogams Port In0

1 - 1

9 Verilogams Port Cb1

14 - SEL1

3 Verilogams Param Con

0

9 Verilogams Port Cb0

13 - SEL0

3 Verilogams Param Coff

20f

9 Verilogams Port Out

17 - OUT

3 Verilogams Param Roff

1T

9 Verilogams Port In11

12 - 12

3 Verilogams Param Ron

0.001

9 Verilogams Port In10

11 - 11

3 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

9 Verilogams Port In9

10 - 10

3 Verilogams Module

AMUXN1

9 Verilogams Port In8

9 - 9

2 Verilogams Port Cb3

16 - SEL3

9 Verilogams Port In7

8 - 8

2 Verilogams Port Cb2

15 - SEL2

9 Verilogams Port In6

7 - 7

2 Verilogams Port Cb1

14 - SEL1

9 Verilogams Port In5

6 - 6

2 Verilogams Port Cb0

13 - SEL0

9 Verilogams Port In4

5 - 5

2 Verilogams Port Out

17 - OUT

9 Verilogams Port In3

4 - 4

2 Verilogams Port In11

12 - 12

9 Verilogams Port In2

3 - 3

2 Verilogams Port In10

11 - 11

9 Verilogams Port In1

2 - 2

2 Verilogams Port In9

10 - 10

9 Verilogams Port In0

1 - 1

2 Verilogams Port In8

9 - 9

9 Verilogams Param Con

0

2 Verilogams Port In7

8 - 8

9 Verilogams Param Coff

20f

2 Verilogams Port In6

7 - 7

9 Verilogams Param Roff

1T

2 Verilogams Port In5

6 - 6

9 Verilogams Param Ron

0.001

2 Verilogams Port In4

5 - 5

9 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

2 Verilogams Port In3

4 - 4

9 Verilogams Module

AMUXN1

2 Verilogams Port In2

3 - 3

8 Verilogams Port Cb3

16 - SEL3

2 Verilogams Port In1

2 - 2

8 Verilogams Port Cb2

15 - SEL2

2 Verilogams Port In0

1 - 1

8 Verilogams Port Cb1

14 - SEL1

2 Verilogams Param Con

0

8 Verilogams Port Cb0

13 - SEL0

2 Verilogams Param Coff

20f

8 Verilogams Port Out

17 - OUT

2 Verilogams Param Roff

1T

8 Verilogams Port In11

12 - 12

2 Verilogams Param Ron

0.001

8 Verilogams Port In10

11 - 11

2 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

8 Verilogams Port In9

10 - 10

2 Verilogams Module

AMUXN1

8 Verilogams Port In8

9 - 9

1 Verilogams Port Cb3

16 - SEL3

8 Verilogams Port In7

8 - 8

1 Verilogams Port Cb2

15 - SEL2

8 Verilogams Port In6

7 - 7

1 Verilogams Port Cb1

14 - SEL1

8 Verilogams Port In5

6 - 6

1 Verilogams Port Cb0

13 - SEL0

8 Verilogams Port In4

5 - 5

1 Verilogams Port Out

17 - OUT

8 Verilogams Port In3

4 - 4

1 Verilogams Port In11

12 - 12

8 Verilogams Port In2

3 - 3

1 Verilogams Port In10

11 - 11

8 Verilogams Port In1

2 - 2

1 Verilogams Port In9

10 - 10

8 Verilogams Port In0

1 - 1

1 Verilogams Port In8

9 - 9

8 Verilogams Param Con

0

1 Verilogams Port In7

8 - 8

8 Verilogams Param Coff

20f

1 Verilogams Port In6

7 - 7

8 Verilogams Param Roff

1T

1 Verilogams Port In5

6 - 6

8 Verilogams Param Ron

0.001

1 Verilogams Port In4

5 - 5

8 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

1 Verilogams Port In3

4 - 4

8 Verilogams Module

AMUXN1

1 Verilogams Port In2

3 - 3

7 Verilogams Port Cb3

16 - SEL3

1 Verilogams Port In1

2 - 2

7 Verilogams Port Cb2

15 - SEL2

1 Verilogams Port In0

1 - 1

7 Verilogams Port Cb1

14 - SEL1

1 Verilogams Param Con

0

7 Verilogams Port Cb0

13 - SEL0

1 Verilogams Param Coff

20f

7 Verilogams Port Out

17 - OUT

1 Verilogams Param Roff

1T

7 Verilogams Port In11

12 - 12

1 Verilogams Param Ron

0.001

7 Verilogams Port In10

11 - 11

1 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

7 Verilogams Port In9

10 - 10

1 Verilogams Module

AMUXN1

7 Verilogams Port In8

9 - 9

0 Verilogams Port Cb3

16 - SEL3

7 Verilogams Port In7

8 - 8

0 Verilogams Port Cb2

15 - SEL2

7 Verilogams Port In6

7 - 7

0 Verilogams Port Cb1

14 - SEL1

7 Verilogams Port In5

6 - 6

0 Verilogams Port Cb0

13 - SEL0

7 Verilogams Port In4

5 - 5

0 Verilogams Port Out

17 - OUT

7 Verilogams Port In3

4 - 4

0 Verilogams Port In11

12 - 12

7 Verilogams Port In2

3 - 3

0 Verilogams Port In10

11 - 11

7 Verilogams Port In1

2 - 2

0 Verilogams Port In9

10 - 10

7 Verilogams Port In0

1 - 1

0 Verilogams Port In8

9 - 9

7 Verilogams Param Con

0

0 Verilogams Port In7

8 - 8

7 Verilogams Param Coff

20f

0 Verilogams Port In6

7 - 7

7 Verilogams Param Roff

1T

0 Verilogams Port In5

6 - 6

7 Verilogams Param Ron

0.001

0 Verilogams Port In4

5 - 5

7 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

0 Verilogams Port In3

4 - 4

7 Verilogams Module

AMUXN1

0 Verilogams Port In2

3 - 3

6 Verilogams Port Cb3

16 - SEL3

0 Verilogams Port In1

2 - 2

6 Verilogams Port Cb2

15 - SEL2

0 Verilogams Port In0

1 - 1

6 Verilogams Port Cb1

14 - SEL1

0 Verilogams Param Con

0

6 Verilogams Port Cb0

13 - SEL0

0 Verilogams Param Coff

20f

6 Verilogams Port Out

17 - OUT

0 Verilogams Param Roff

1T

6 Verilogams Port In11

12 - 12

0 Verilogams Param Ron

0.001

6 Verilogams Port In10

11 - 11

0 Verilogams Library

module AMUXN1 (in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3);

electrical in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, out, CB0, CB1, CB2, CB3, AVDD, GND, EN, out_int;

input in0, in1, in2, in3, in4, in5, in6, in7, in8, in9, in10, in11, CB0, CB1, CB2, CB3, AVDD, GND, EN;

output out;

parameter real Ron = 0.001;

parameter real Roff = 1T;

parameter real Coff = 20f;

parameter real Con = 0;

parameter real offTr;

parameter real onTr;

integer channel;

real RCH0 = Roff;

real RCH1 = Roff;

real RCH2 = Roff;

real RCH3 = Roff;

real RCH4 = Roff;

real RCH5 = Roff;

real RCH6 = Roff;

real RCH7 = Roff;

real RCH8 = Roff;

real RCH9 = Roff;

real RCH10 = Roff;

real RCH11 = Roff;

real CCH0 = Coff;

real CCH1 = Coff;

real CCH2 = Coff;

real CCH3 = Coff;

real CCH4 = Coff;

real CCH5 = Coff;

real CCH6 = Coff;

real CCH7 = Coff;

real CCH8 = Coff;

real CCH9 = Coff;

real CCH10 = Coff;

real CCH11 = Coff;

real VTH;

endmodule

6 Verilogams Port In9

10 - 10

0 Verilogams Module

AMUXN1

Show More

Show Less

Design Files